Learning About FPGAs in Finance

Learning About FPGAs in Finance

If you have spent any time in FPGA design, you have probably heard that high-frequency trading pays well. What is less commonly understood is why FPGAs specifically dominate this space, what the engineering work actually looks like, and what it takes to land one of these roles.

This article pulls together insights from engineers who have worked at HFT firms, technical documentation from FPGA hardware vendors, and practitioner accounts from the quant and FPGA engineering communities.

Why Finance Needs Hardware-Level Speed

The core premise of high-frequency trading is straightforward: if your order reaches an exchange before a competitor's, you get the trade. Competitive advantage is entirely a function of latency, measured in nanoseconds.

Software-based trading systems running on CPUs and general-purpose operating systems typically operate in the millisecond range. Even a carefully tuned Linux kernel running a C++ trading engine on a co-located server has to deal with interrupt handling, OS scheduling jitter, and memory hierarchy effects that introduce variability of tens of microseconds at best.

FPGAs change the equation entirely. By implementing order logic, market data parsing, and protocol handling directly in hardware, trading firms can achieve round-trip latencies below 100 nanoseconds, from network ingress to order emission. There is no OS, no scheduler, no cache hierarchy interfering with the critical path. Data moves through a deterministic pipeline at line rate.

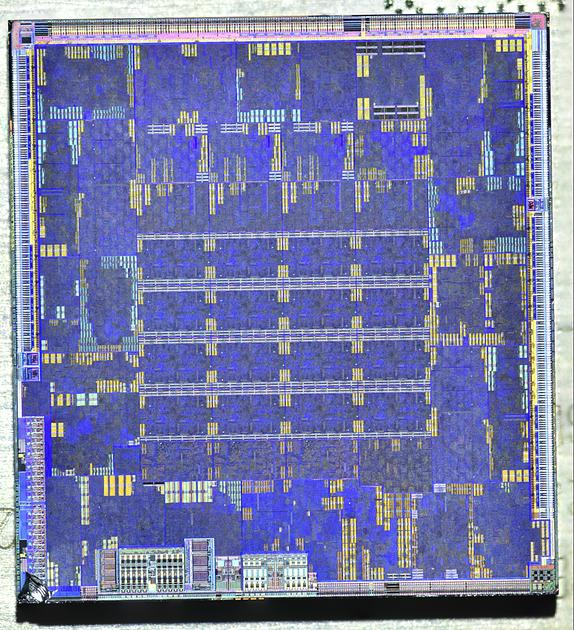

AMD's Alveo UL3422 FinTech accelerator, built on a 16nm silicon node, illustrates where dedicated trading hardware has landed. It delivers up to 7x lower latency than its predecessor and integrates an ultra-low latency Ethernet MAC directly on the card. The card sits between the network and the trading algorithm, filtering incoming market data at wire speed before handing relevant updates to the decision layer, all without touching the host CPU.

The key architectural idea is inline processing at network speeds. Rather than buffering a complete market update and parsing it afterward, an FPGA examines the data stream as it arrives. Many exchange protocols (ITCH, OUCH, FIX FastPitch) use fixed-format messages, so the byte position of a price field is known at design time. The FPGA can extract only the fields it needs without decoding the full message, cutting latency to the minimum imposed by propagation delay and combinational logic depth.

The Full HFT Engineering Stack

It is a common misconception that FPGA engineers in HFT write self-contained algorithms that run entirely in hardware. In practice, the architecture is a layered system.

At the base sits the FPGA, handling market data feed parsing, order entry, and network protocol management. Above it runs a Linux host system with a trading engine written in C++, C#, or Java, managing strategy logic, position tracking, and risk controls. Human traders and quant researchers sit above that layer, monitoring the system in real time and adjusting parameters through a UI or Python API.

The FPGA fires on triggers: predefined conditions derived from the parsed market feed. When price levels or order book states match a programmed condition, the FPGA emits an order with no CPU involvement. The trigger conditions themselves are configured by the software layer. Risk management software on the CPU can automatically throttle or disable those triggers if position thresholds are breached.

For FPGA engineers, this means the work centers on minimizing critical path depth, managing resource utilization on Ultrascale+ devices, and implementing testable RTL that can absorb rapid changes. Technical debt management matters because firms need the ability to push a hotfix to a live system during market hours. A messy codebase with poorly documented timing constraints is a liability when you need to make a one-line change at 9:30 AM.

What FPGAs Can and Cannot Do in Trading

FPGAs are well-suited to strategies operating at the highest frequencies: market making, latency arbitrage, and statistical arbitrage on tick data. These strategies tend to be simple in algorithmic terms, which is necessary because logic complexity and latency are in direct tension. Every additional LUT on the critical path costs nanoseconds. A strategy requiring complex arithmetic, deep state machines, or ML inference may not be implementable within a competitive latency budget.

This creates a hard ceiling on what FPGAs can execute autonomously. Strategies requiring longer lookback windows, large state, or iterative computation shift to the CPU layer or off the FPGA entirely. The split is practical, not philosophical.

Capacity is the other constraint. HFT has a fundamental ceiling on assets under management: a strategy that makes money by being the fastest order in the book cannot scale to tens of billions of dollars. This is why the largest HFT firms (HRT, Tower Research, Citadel Securities) also operate mid-frequency and lower-frequency trading desks that run entirely on CPUs, target longer holding periods, and manage far larger positions. The FPGA team and the software quant team often coexist within the same firm but work on entirely different problems.

AI and ML are beginning to enter the picture. AMD and other vendors are enabling ML model integration directly on trading cards, allowing inference to run on-chip alongside the protocol stack. As raw latency gains become harder to achieve at the physics level, the industry is shifting toward asking whether the same hardware can make smarter decisions rather than just faster ones.

Who Is Hiring and Where

HFT firms hiring FPGA engineers cluster around two financial centers in the US: New York and Chicago. London, Amsterdam, and Singapore are significant markets outside North America.

Firms with known FPGA engineering practices include Optiver (Amsterdam-headquartered, offers structured FPGA internships), IMC (active in equities and options, publishes technical content on FPGA use in trading), Citadel Securities (large-scale operation with deep low-latency infrastructure investment), Tower Research Capital (expanding from HFT into mid-frequency strategies), and Hudson River Trading.

Firm size matters when evaluating opportunities. Engineers who have worked in the space consistently recommend targeting mid-size firms with a dedicated FPGA team. At the largest firms, individual contributors can become interchangeable; at firms without a real FPGA practice, you may find yourself working in isolation without meaningful tooling or mentorship. The sweet spot is a firm that takes FPGA seriously enough to invest in it but is small enough that your work has visible impact.

For a view of what FPGA and semiconductor design roles look like across the broader market, the ASIC Design Jobs section of this board includes openings across finance, networking, and compute.

What Skills HFT Firms Actually Want

Based on recruiter and practitioner accounts from the FPGA engineering community, the skill profile for HFT FPGA roles looks like this.

Required: end-to-end RTL project experience (not just component-level work), Verilog and SystemVerilog (VHDL for legacy-heavy shops), familiarity with Xilinx/AMD Ultrascale+ devices, Python and C for testbenches and integration tooling, and experience with real-time systems and high clock speed design.

Valuable: custom IP development (memory controllers, high-speed serial interfaces), PCIe and 10/25/100G Ethernet experience, exchange protocol implementation (ITCH, OUCH, FIX), and simulation methodology for deterministic systems.

Not required: a finance or economics background, knowledge of trading strategy theory, or quantitative finance credentials.

That last point surprises engineers who assume finance roles require finance knowledge. They do not, at least not on the FPGA side. Firms want engineers who can ship correct, fast, testable RTL. The trading strategy is handled by a separate quant team. The FPGA engineer's job is hardware, and HFT firms pay a meaningful premium for people who do it well.

For context on how FPGA-focused careers compare to ASIC and verification tracks across the broader semiconductor industry, the semiconductor design career guide covers the landscape in detail.

Compensation and Culture

FPGA engineers at HFT firms earn 30 to 60 percent more in total compensation than counterparts at traditional semiconductor companies. Base salaries are competitive with large-cap tech; the differential comes primarily from bonuses. Bonuses start at roughly $20,000 at entry level and have no practical ceiling. Engineers with multiple years of tenure at successful firms have reported bonus payouts exceeding $500,000 in strong years.

The tradeoffs are real. Standard schedules run 10 to 12 hours per day. Engineers close to live trading systems are effectively on call during market hours. Perks like unlimited vacation exist formally but are culturally difficult to exercise in an environment where system uptime is a direct competitive variable.

Garden leave is standard. When an engineer with access to trading algorithms or system architecture leaves a firm, the firm typically pays 3 to 18 months of salary to enforce a non-compete period. This protects IP and normalizes slow, deliberate job transitions. Engineers in this space plan moves well in advance.

The industry is small. FPGA engineers at HFT firms tend to know each other across companies. Professional reputation is a meaningful career asset in a community where hiring is often relationship-driven.

It is also worth noting that FPGA skills developed in HFT transfer well. Low-latency networking, deterministic RTL design, protocol implementation, and real-time systems experience are all valued in telecom, datacenter networking, aerospace, and industrial automation. Leaving HFT does not mean leaving FPGA work.

Breaking In

The entry path most commonly cited by practitioners is a combination of strong project-based RTL work and targeting firms with formal internship programs. Optiver's FPGA internship is well-known in the community and frequently mentioned as an accessible entry point. IMC and similar firms recruit from EE and computer engineering programs with serious digital design curricula.

If you are building the foundational skills needed to compete for these roles, the book Trading at the Speed of Light by Donald MacKenzie is recommended as a non-technical overview of the HFT industry. It provides the strategic context that helps FPGA engineers understand why the latency constraints they work under exist. There is no single technical reference specifically on FPGA design for HFT, which reflects both the competitive secrecy in the space and the fact that the core competencies are simply applied FPGA design: RTL, timing closure, IP integration, and high-speed interfaces.

Understanding the full chip design ecosystem, including where FPGAs sit relative to ASICs and how both fit into the broader electronics supply chain, is also useful background. The guide to how chips are made covers that foundation in detail.

Conclusion

FPGAs in finance are not a niche curiosity. They are the operational foundation of a significant portion of global equity and options market activity. For FPGA engineers seeking technically demanding, well-compensated work, HFT firms represent one of the strongest compensation opportunities in the industry. The barrier to entry is technical skill, not financial background, and the skills transfer broadly.

If you are exploring FPGA and semiconductor design roles across finance, networking, and compute, browse current semiconductor design openings to see what is hiring now. The semiconductor salary guide also provides compensation benchmarks across disciplines if you want to evaluate where HFT stacks up against other markets.